DigisparkのPLLとlow-pass filterとアンプと [Arduino]

上位のArduino Uno(ATmega328)にはなくて、Digispark(ATtiny85)にはあるものとして、PLL(位相同期回路: phase locked loop)があります。

まず、使用するには、、

PLLCSR(PLL Control and Status Register)

Bit 1 - PLLE: PLL Enable はシステムクロック元としPLLが選択されているので元々1。

Bit 2 - PCKE: PCK Enable を1にすることで、タイマー/カウンタ1のクロック元をPLLにします。

Bit 7 - LSM: Low Speed Mode(32MHz) ですが、そのまま 0 で高速モード(64MHz)。

・注意点

★システムクロック(16/8/1MHz)に関わらず64MHz(LSM: Low Speed Mode時は32MHz)

(ただしOSCCAL (Oscillator Calibration Register)をいじるとシステムクロックと一緒に微調整はできます)

★タイマー/カウンタ1だけ

(ただしDigisparkではボードマネージャでDigistump AVR Boardsの場合でISR(TIMER1_OVF_vect)が使用されてしまっている)

・使用用途

とりあえず、高速PWMによる疑似DACかな。

64MHz / 256(8bit) = 250kHz が、キャリア周波数ということでした。

まあ、Uno(16MHz)で9bitだと 16MHz / 512(9bit) = 31.25kHz だとノイズらしいノイズは分かりませんでしたが、半分の15.625kHzだとノイズが分かりました。

あと、外部出力の際には、low-pass filterがないとアンプが壊れるよっていうのが各所に書いてありました。

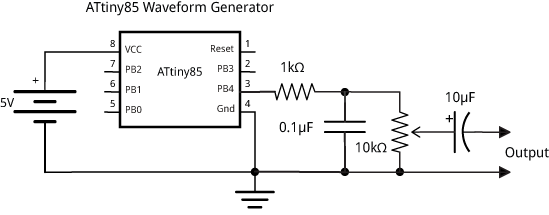

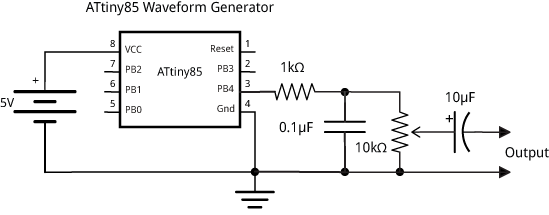

low-pass filterの具体的な値の計算式は理解できなかったので、以下のサイトのPLL音声出力時の回路図を参考とさせていただきました。

PB4(OC1B)から1kΩの抵抗と、そこからGNDとの間に0.1μFのコンデンサとなっていました。

Technoblogy - Waveform Generation using an ATtiny85

http://www.technoblogy.com/show?QVN

とか

Technoblogy - Four Sample Player

http://www.technoblogy.com/show?2XJD

また、次のページには、PB4(OC1B)から220μFの電解コンデンサを介してスピーカとつないでありました。

Technoblogy - Tiny Synth

http://www.technoblogy.com/show?Q7H

他では、100μFだったりするのもありました。

Technoblogy - Audio Pitch Shifter

http://www.technoblogy.com/show?1L02

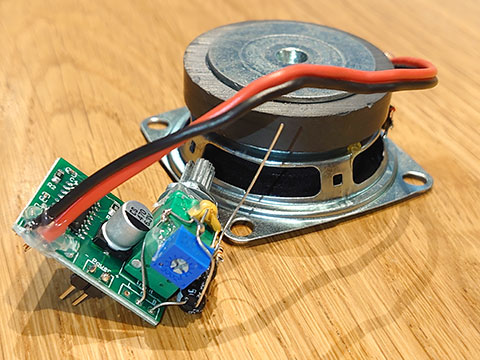

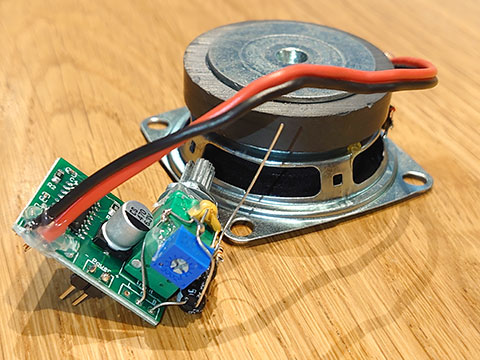

できあいのアンプとつないでみました。

そのままアンプにつなぐと、音が大きすぎて音が割れるので、回路図のとおり10kΩの半固定抵抗をつけました。

まず、使用するには、、

PLLCSR(PLL Control and Status Register)

Bit 1 - PLLE: PLL Enable はシステムクロック元としPLLが選択されているので元々1。

Bit 2 - PCKE: PCK Enable を1にすることで、タイマー/カウンタ1のクロック元をPLLにします。

Bit 7 - LSM: Low Speed Mode(32MHz) ですが、そのまま 0 で高速モード(64MHz)。

・注意点

★システムクロック(16/8/1MHz)に関わらず64MHz(LSM: Low Speed Mode時は32MHz)

(ただしOSCCAL (Oscillator Calibration Register)をいじるとシステムクロックと一緒に微調整はできます)

★タイマー/カウンタ1だけ

(ただしDigisparkではボードマネージャでDigistump AVR Boardsの場合でISR(TIMER1_OVF_vect)が使用されてしまっている)

・使用用途

とりあえず、高速PWMによる疑似DACかな。

64MHz / 256(8bit) = 250kHz が、キャリア周波数ということでした。

まあ、Uno(16MHz)で9bitだと 16MHz / 512(9bit) = 31.25kHz だとノイズらしいノイズは分かりませんでしたが、半分の15.625kHzだとノイズが分かりました。

あと、外部出力の際には、low-pass filterがないとアンプが壊れるよっていうのが各所に書いてありました。

low-pass filterの具体的な値の計算式は理解できなかったので、以下のサイトのPLL音声出力時の回路図を参考とさせていただきました。

PB4(OC1B)から1kΩの抵抗と、そこからGNDとの間に0.1μFのコンデンサとなっていました。

Technoblogy - Waveform Generation using an ATtiny85

http://www.technoblogy.com/show?QVN

とか

Technoblogy - Four Sample Player

http://www.technoblogy.com/show?2XJD

また、次のページには、PB4(OC1B)から220μFの電解コンデンサを介してスピーカとつないでありました。

Technoblogy - Tiny Synth

http://www.technoblogy.com/show?Q7H

他では、100μFだったりするのもありました。

Technoblogy - Audio Pitch Shifter

http://www.technoblogy.com/show?1L02

できあいのアンプとつないでみました。

そのままアンプにつなぐと、音が大きすぎて音が割れるので、回路図のとおり10kΩの半固定抵抗をつけました。

2022-06-19 18:32

nice!(0)

コメント(0)

コメント 0